LCDs(lvds) on RK3568 Bring-Up 数据流研究

Categories:

少于1分钟

背景知识

- 参考:How-to: 显示接口调试标准工作流程 (SOP)

- 参考:Rockchip显示子系统关键概念解析

- 举例: 以lvds为例

数据流-(硬件的视角)

- 好了,这一步就是要确定硬件是怎么接的,我们直接梳理整个数据流的图形

1. 数据从内存->vop

不论是从外设进来的,还是emmc上的, 都要搬进内存.所以数据流的起点是内存. 这里从内存给到vop里配置的那个具体的vp.在dts里配置vop的代码如下:

&lvds_in_vp2 {

status = "okay";

};

此处是以vp2为最终lvds要关联的vp,但是并不是每个soc/或者每次产品的应用场景都是vp2的.

- How-to: 如何确定接口的数据是从哪一个vp出去的呢?

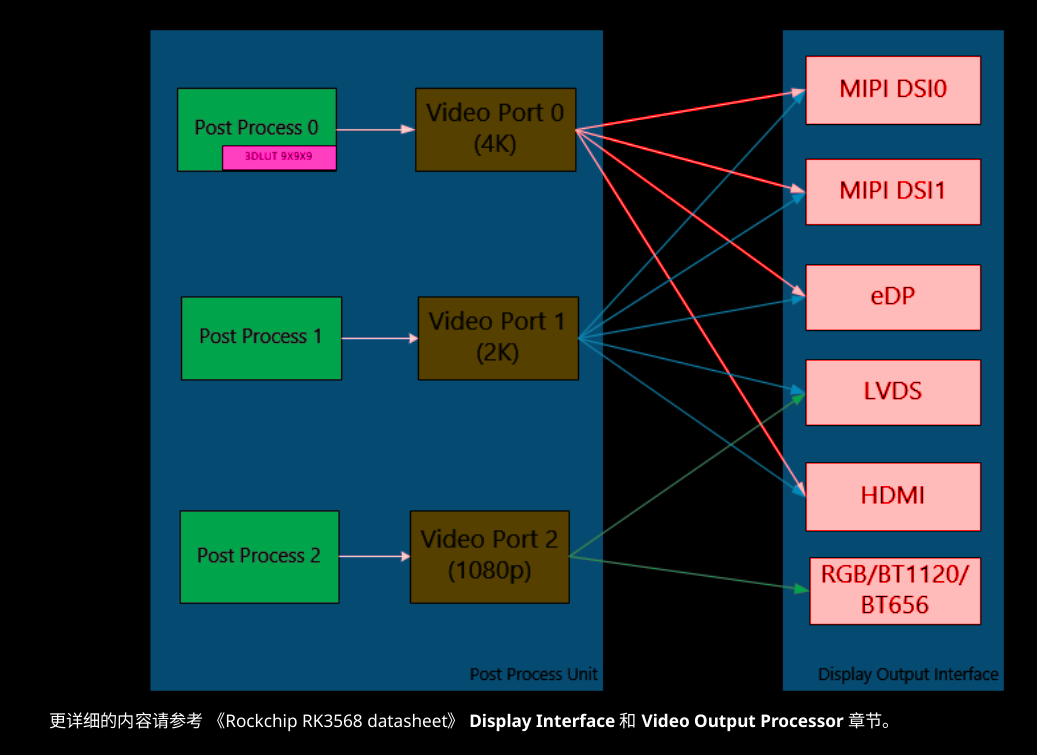

- 要从rk的这份图来看

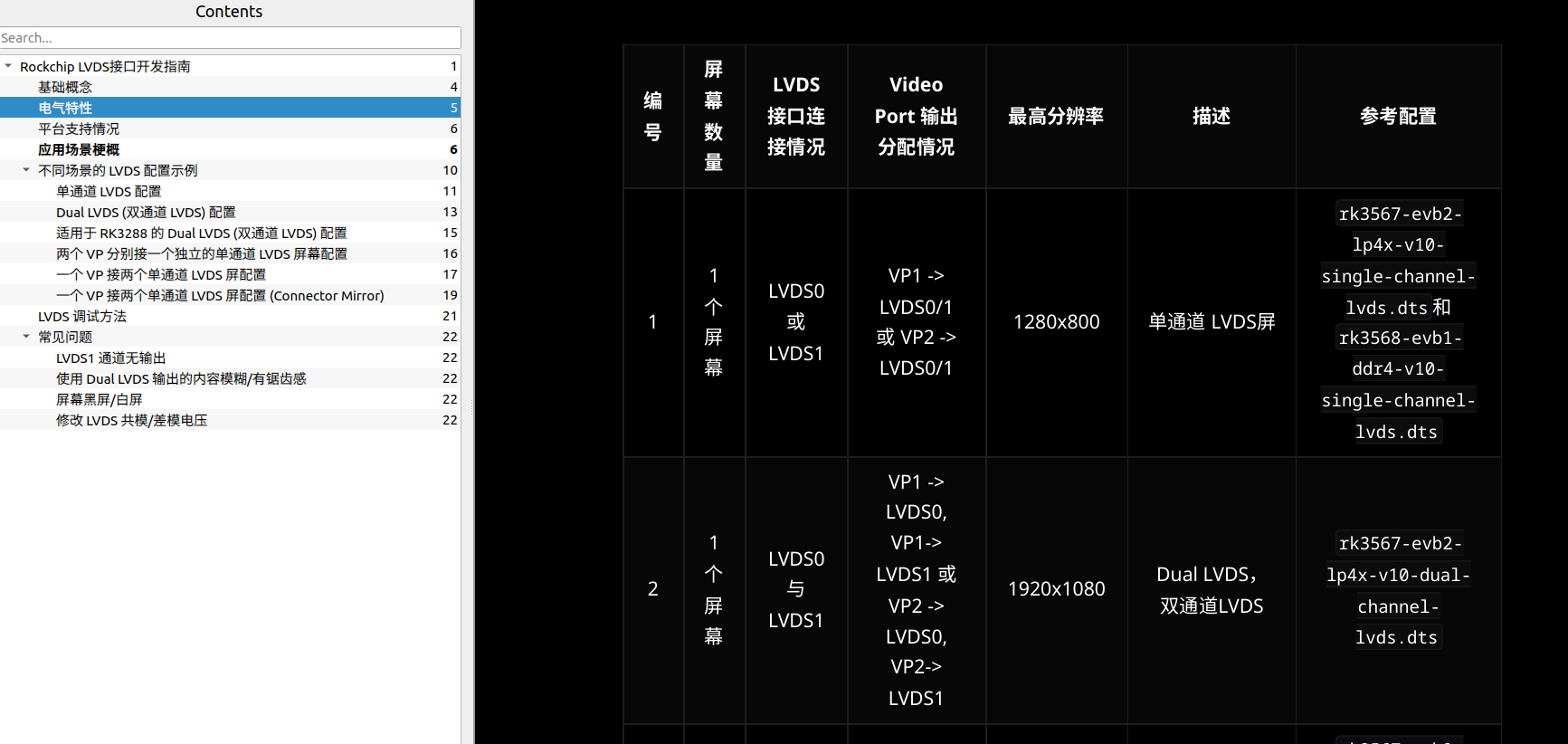

- 它规定了lvds只能走vp1或vp2,但因为我们的系统需要3个屏幕,且vp0~2的性能是越来越弱, 因此lvds的频率关系就决定了它最合适使用vp2.

- 在这里要注意,其实这里写着1080p并不是代表lvds(以此为例)就能够到1080p.它还跟lvds本身有单通道和双通道有关系

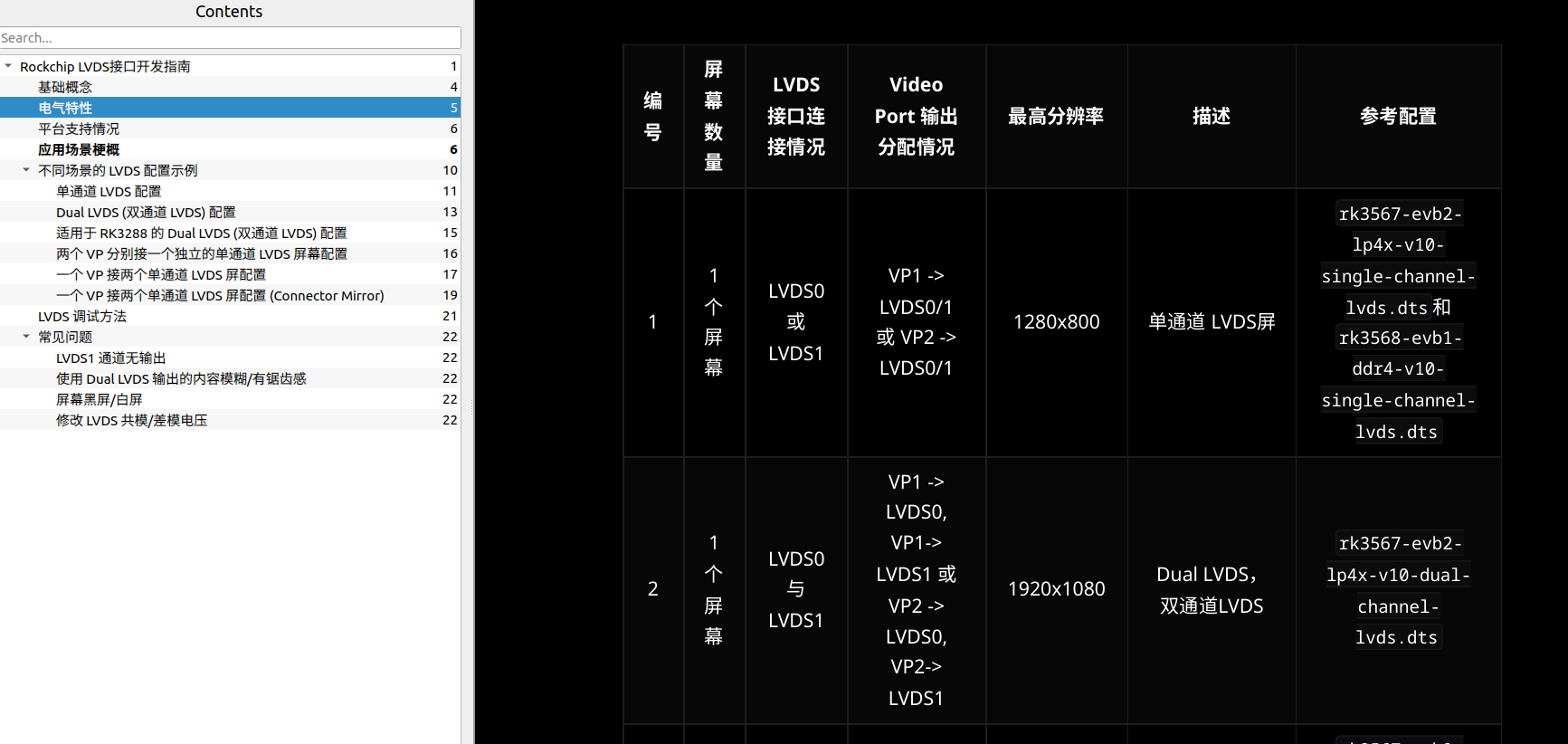

- 要从rk的这份图来看

2. [逻辑配置][硬件不存在]信号抵达route_lvds这个"路由器"

&route_lvds {

status = "okay";

connect = <&vp2_out_lvds>;

};

在这里, 设备树中配置让lvds可以连接到router. 这里需要深度去研究一下rk3568内部的封装, AI说这里的router是一个实际存在的IP, 就专门用来关联到不同的display interface.(这里的interface是一个抽象的逻辑概念, 物理上一般由controller和对应的phy组成,例如mipi DSI Host Controller对应mipi_tx dphy)不过,因为没有Rockchip公司给出的资料或者芯片手册中切实的证据去反推这个IP的存在,因为在此,还是把route_lvds作为一个逻辑上存在的概念最安全.

- 补充

- 这张图实际上在佐证route非常可能是一个独立的IP存在,很可能具备可写的寄存器.才能实现引入不同display interface的功能.

3. 再从vop->lvds控制器

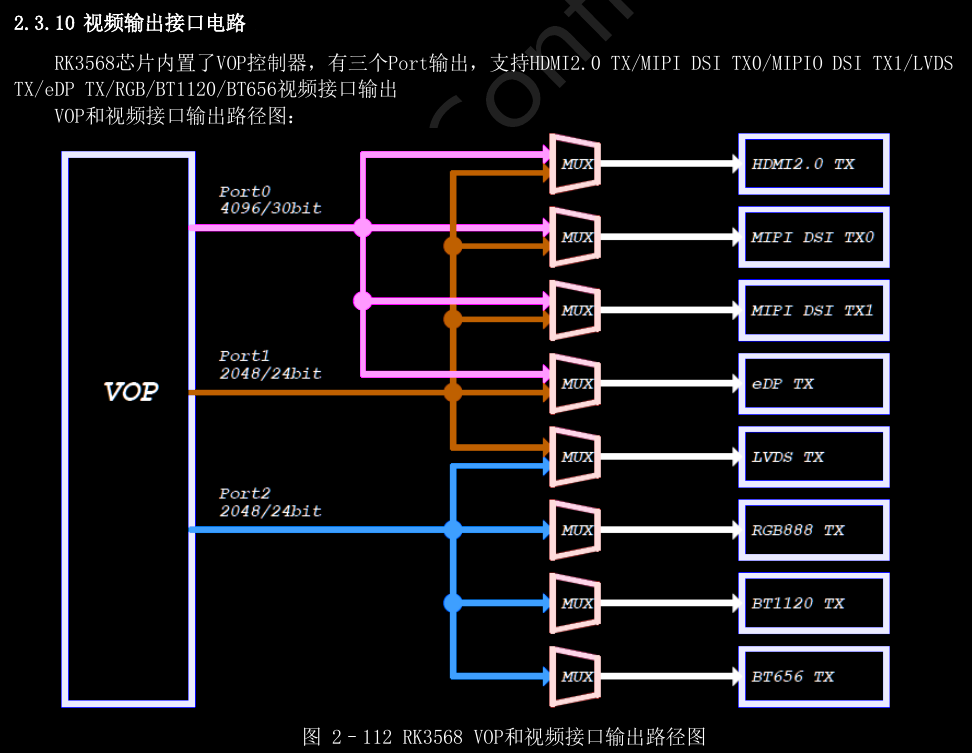

- 在RK3568的设计中,LVDS控制器并非一个像MIPI-DSI那样独立的复杂IP核。它的核心控制逻辑被简化并内嵌到了VOP和GRF(通用寄存器文件)中.这一点是靠数据手册里的寄存器介绍和原理介绍反推的.

- 通过特定的寄存器位来进行配置GRF_VO_CONF0和GRF_VO_CONF2.所以可以参考

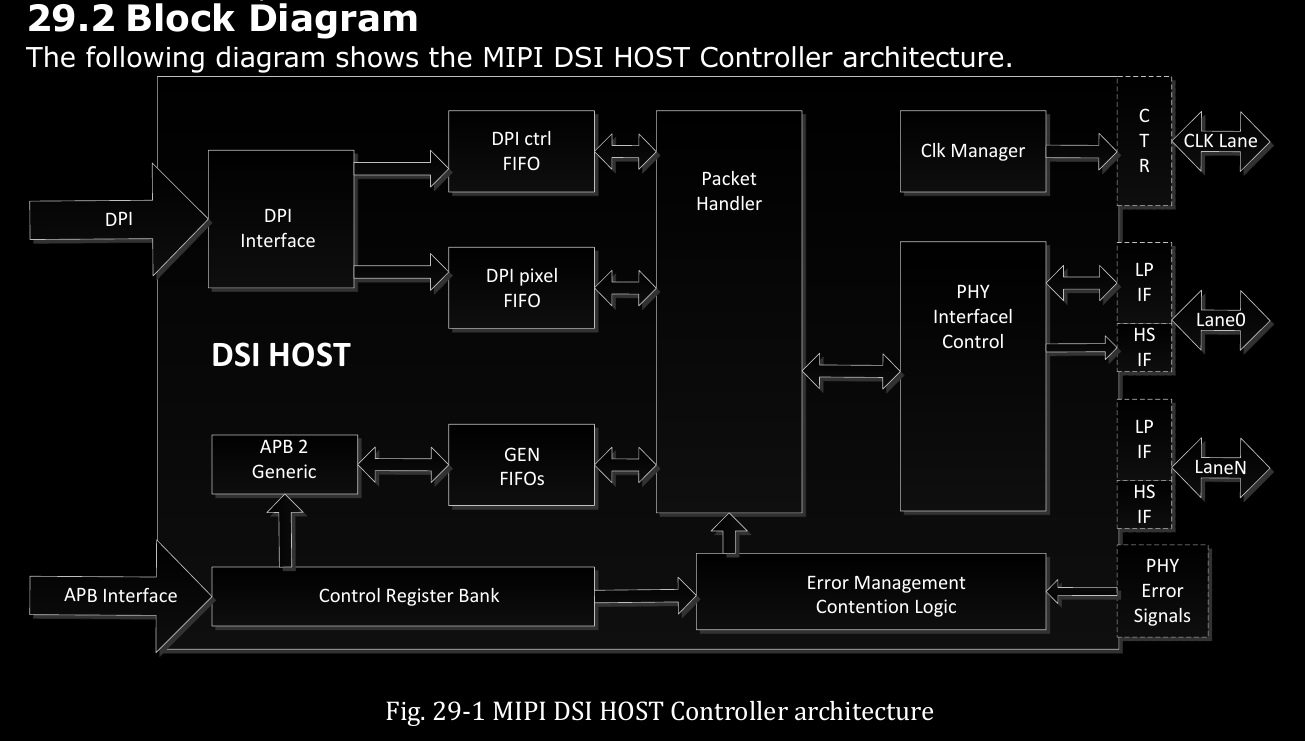

- 参考MIPI-DSI控制器的架构图,我们可以清晰地看到数据流的末端有一个PHY Interface Control。这表明,**控制器(Controller)的角色是在VOP的通用视频和PHY的物理层之间,扮演一个“协议转换和打包”**的角色。它接收来自VOP的RGB数据,并按照LVDS的bus-format(如SPWG/JEIDA)规则将其打包,然后送给PHY。

# 在panel中设置

bus-format = <MEDIA_BUS_FMT_RGB888_1X7X4_JEIDA>;

4. 从lvds控制器->MIPI-DPHY

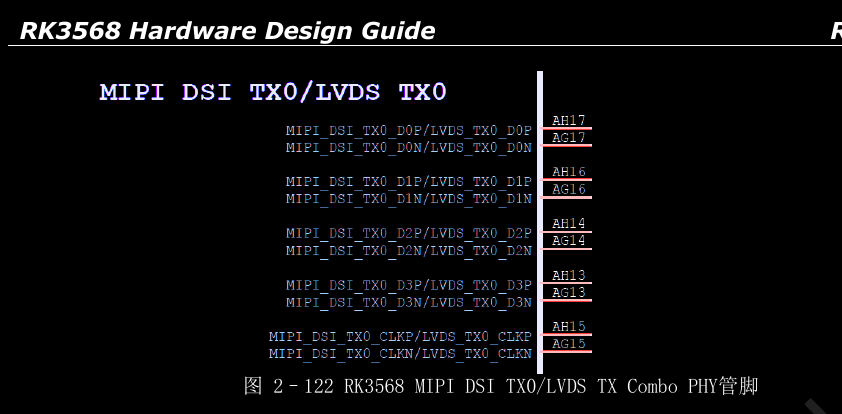

- 3568里, mipi0和lvds0是共用一套phy的, mipi1和lvds1又是共用一套phy.可参考

- 然后会按照设备树里配置的vp输出去.最终输出去就是按照GRF寄存器里定义的那几个引脚, 这几个引脚就是PHY的引脚, 是不可配置的, 不会出现在GPIO中.

- 设备树的代码如下:

- &lvds节点编辑的时候,phys=<&video_phy0>;

- 并且让video_phy0的status=“okay”.

// 2. 使能lvds对应的物理层PHY &video_phy0 { status = "okay"; }; // 3. 完整配置LVDS控制器 &lvds { status = "okay"; phys = <&video_phy0>;}

- 这么做就表明是让lvds走phy0了. 当然,在dts里,phy0不是一个被设置为某一个接口的视角, 而是被谁使用的一个角色, 是一个静态客观不变的角色.而这个phy和接口电路的映射关系其实也是固定的,在soc里面被做好的,做成可配置罢了.

5. PHY给到LCD

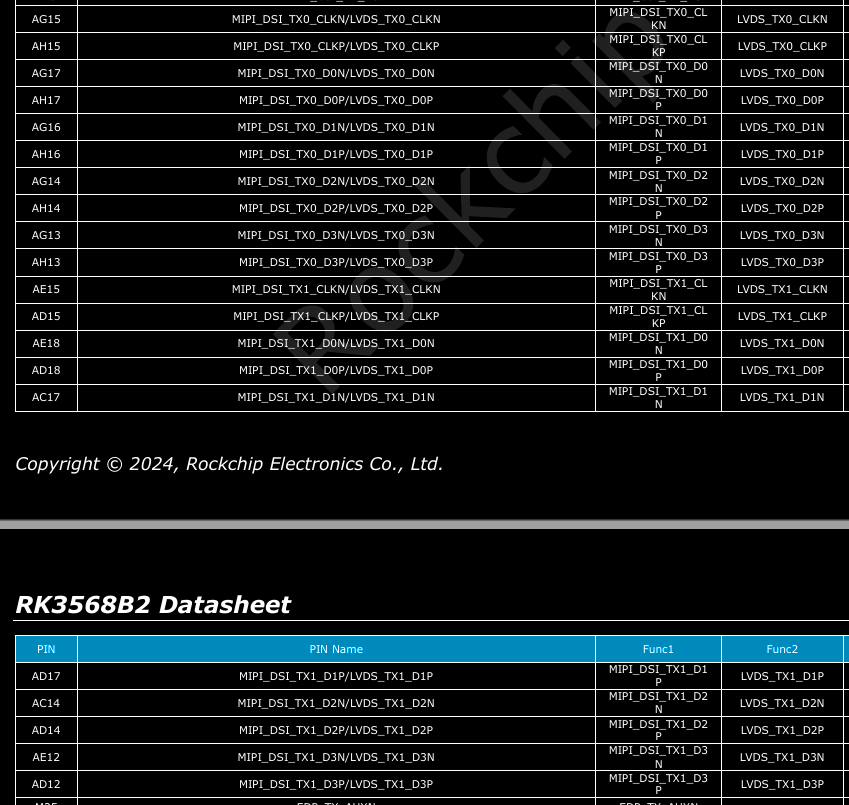

图中的这些引脚(例如AG17/AH17等)都是PHY直接给出到显示屏幕的引脚, 也是soc这边的数据流的最后一个部分.

lvds接口中, 4对数据脚(差分),1对时钟脚(差分), 对端按照lvds协议进行接收, 如果一切正确, 就能够显示内存中的图像了.

图中的这些引脚(例如AG17/AH17等)都是PHY直接给出到显示屏幕的引脚, 也是soc这边的数据流的最后一个部分.

lvds接口中, 4对数据脚(差分),1对时钟脚(差分), 对端按照lvds协议进行接收, 如果一切正确, 就能够显示内存中的图像了.

本次总结

本次对接的是fpga,即fpag作为我的一个dummy screen.最终fpga那边成功的分辨率和帧率是1920x1080p30.

但是据RK官方的文档来说,最高的分辨率仅仅1280x800

所以, 可以得出lvds的控制器并没有对hactive或vactive进行限制, 更进一步说,很可能是时钟频率满足(不高于vp2和mipi_dsi_tx_dphy的最高限制)的情况下,是可以打到极限的.

但是换一块屏幕是否能达到, 可能并不一定.

所以, 可以得出lvds的控制器并没有对hactive或vactive进行限制, 更进一步说,很可能是时钟频率满足(不高于vp2和mipi_dsi_tx_dphy的最高限制)的情况下,是可以打到极限的.

但是换一块屏幕是否能达到, 可能并不一定.